算力困境:谁能成为高性能计算的助推器?

作者:admin 来源:半导体行业观察 发布时间:2023-11-29 访问量:2827

当今我们正处于一个算力需求极速增长的时代,无论是ChatGPT的火爆,还是各种高性能计算(HPC)的兴起,背后都是无尽的算力需求。很明显,单片SoC在处理、内存、带宽各方面都或多或少面临着不同程度的挑战,已经不能满足这些强劲的需求。那么,谁能成为高性能计算的助推器呢?

近年来,异构集成、Chiplet等多芯片系统(Multi-Die)开始发挥重要作用,并呈现出明显增长趋势。Multi-Die系统通过将多个不同功能、甚至不同工艺制程的裸片组合在一起,为芯片系统的功率、性能和良率都带来了新的提升路径。但是要想确保Multi-Die系统的可靠性和成功,不是易事。为此,行业内各界人士正在为Multi-Die技术的快速发展出谋划策。

Multi-Die系统可靠性要过“两大关”

与传统的单芯片相比,Multi-Die的健康和可靠性有两大至关重要的关隘。

第一大关,验证各个裸片性能的良好程度。任何一个裸片的失败都会导致整个系统的失败,所以首先要保证每个裸片都经过详尽测试,达到极低的故障率。

影响芯片性能的因素有很多,如温度、老化和退化等。特别是在Multi-Die系统中,不同工艺节点的芯片可能会有不同的工作温度和散热需求,芯片间的电磁干扰和电迁移问题也需要关注。因此我们需要进行系统级评估。在Multi-Die系统中,预组装测试至关重要,可以帮助确认已知良好的芯片(KGD)。此外,先进的可测试设计(DFT)功能集成,也可以用来确保芯片的全面评估。

第二大关,验证芯片间接口的高效性能。这些接口是系统整体性能的关键,尤其在高带宽、高能效和低延迟的接口设计中更为显著。假如采用了3D堆叠设计,由于互连的长度更短,硅通孔(TSV)的脆弱性增加,使得互连级风险上升。通常,这些高速接口基于UCIe等标准,适用于各种封装类型,支持高速传输,适用于从网络到大规模数据中心的应用。因此,确保小芯片之间的接口无固定故障、开路或短路,以及从时序和电压角度的正确行为,对于确保数据的有效共享至关重要。UCIe提供的冗余通道能在必要时进行修复,确保基于UCIe的系统中的芯片能够被有效访问、测试和修复。

可以看出,对单个芯片到整个系统,以及裸片之间的互联特性进行全面测试,对于确保Multi-Die系统设计的可靠性和性能至关重要。但是要过这两大关,达成这样完整性测试,对于行业来说,具有一定的挑战。Multi-Die系统的测试和监控必须转向更高级、集成化的解决方案。

全生命周期管理(SLM):Multi-Die系统成功的关键

随着芯片和系统复杂性的不断增加,以及对产品性能和寿命的更高期望,为半导体的设计、制造和部署定义了新的边界限制。例如,在Multi-Die系统设计中,基于UCIe微凸块的距离通常在25~55微米,而传统的物理方法所能探测的距离一般为90微米。这就意味着传统的物理探测技术无法足够接近微凸块以进行有效测试。因此,面对Multi-Die系统这样的新需求,必须要找到一种行之有效的方法。

硅生命周期管理(SLM)方法是业内新兴的一种范例,是SoC和其他先进半导体的生产、制造和部署流程中越来越重要的组成部分。SLM方法使半导体设计能够利用“监控、分析和优化”的理念,提高硅系统的质量、性能和可靠性,实现预测性维护和故障预测。SLM的核心主要体现在以下两点:

通过在芯片设计过程中集成传感器和监视器,评估温度、电压、老化和退化等参数,这将特别适用于开发阶段和现场使用的系统。

在硅设备的整个生命周期中收集和分析数据,以提供强大的分析功能,从而实现设计中、测试中和现场观察以及设备改进;

这种全生命周期洞察的思维也为Multi-Die系统的设计和发展带来了显着的功能和性能优势。以热问题为例,这是单个芯片和多芯片系统所共同关注的。以往在设计阶段很难在没有实际工作负载的情况下评估这些问题。当引入2.5D或3D架构时,了解最终设计的热分布变得更加困难。而借助SLM方法,在芯片上有策略性地放置监视器,可以为分析提供数据,进而提供对芯片热特性的深入了解,指明可能需要调整布局以解决散热问题的地方。

SLM技术的另一个优势是可追溯性,无论最终产品在其生命周期中何时出现问题,都能追溯到问题的根源。这对于多芯片系统尤为重要,因为其封装成本极高,越早发现问题,最终损失越小,且能够更快地投入市场。

此外,在最终产品出现故障的情况下,SLM也能发挥作用。通过测试和分析整个制造生态系统,可以确定故障的根本原因,并识别可能表现出类似问题的设备,从而实现主动召回或通过调整工作电压或频率来延长设备寿命。

在硅生命周期管理(SLM)领域,新思科技正成为该领域的重要贡献者。新思科技所开发的SLM监控和分析技术,涵盖了全面的集成工具、IP和方法,并将其整合到一个统一的平台中。通过智能、高效地收集和存储整个Multi-Die系统生命周期中的监控数据,并通过使用强大的分析提供操作建议,为Multi-Die系统的设计研发保驾护航,进而满足客户和合作伙伴生态系统的需求。

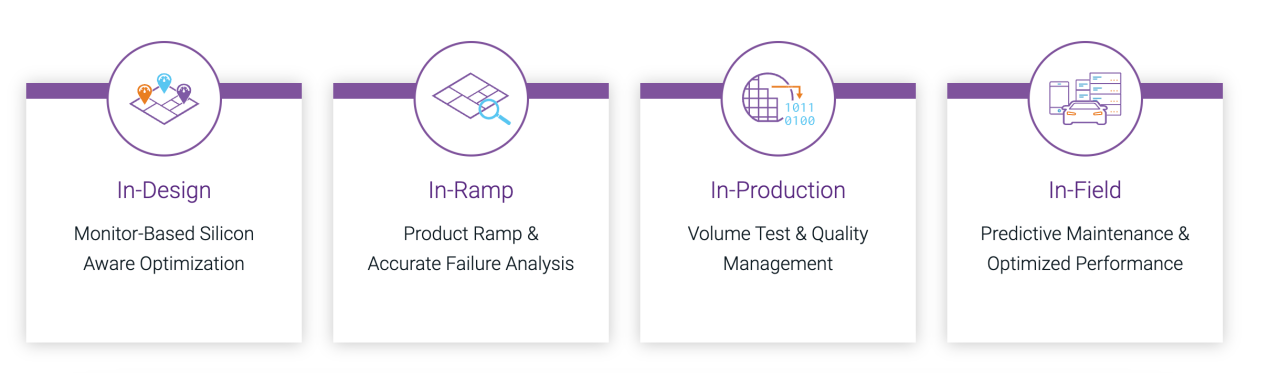

新思科技的SLM解决方案贯穿整个芯片生命周期的每个阶段

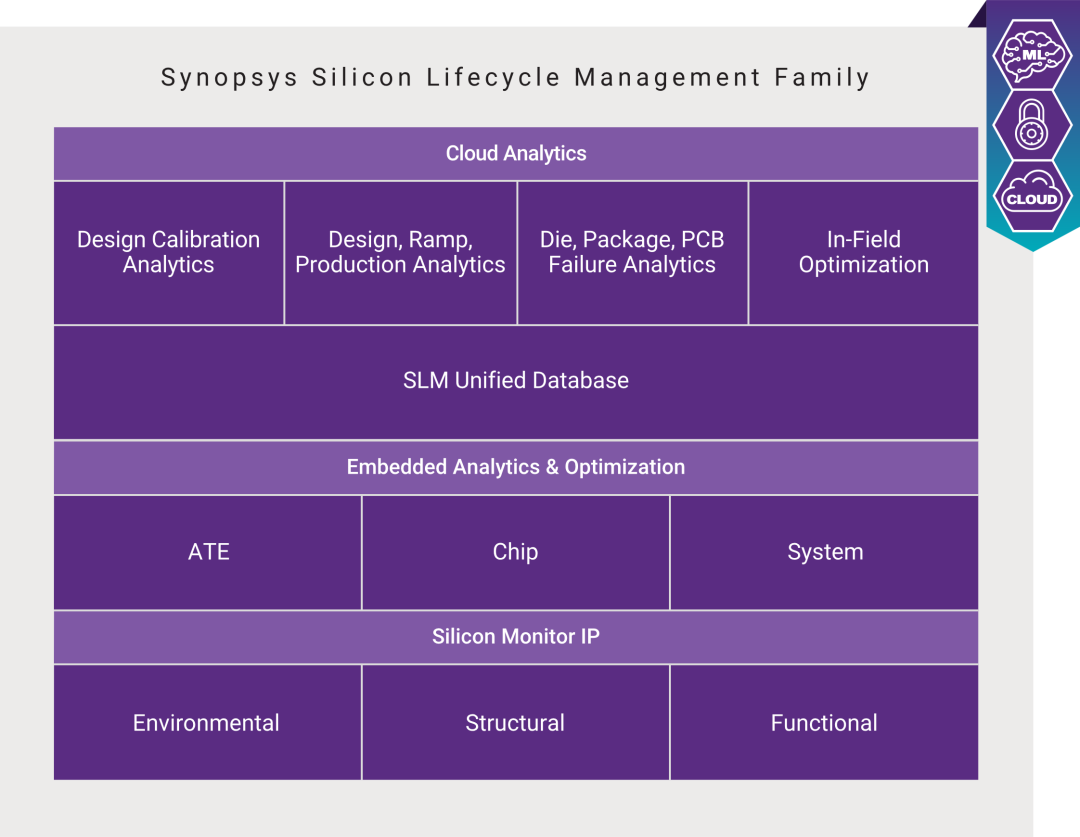

如下图所示,新思科技的SLM家族中的SLM PVT监视器IP,可实时收集数据,用于优化和故障诊断,PVT监视器IP已通过SGS-TÜV Saar认证,并符合AEC-Q100级标准;基于AI的优化技术可提高设计性能和可靠性;所有的SLM集成系统都建立在统一的数据库解决方案之上,可提高数据可见性和分析效率。最终形成了一个端到端解决方案,可满足所有SLM要求。

新思科技的SLM家族

助力Multi-Die系统走向更高峰

在高性能计算的推动下,Multi-Die系统的发展正在加速。但是,Multi-Die系统作为半导体行业的新兴技术,要想广泛推广和进一步发展,仍需在设计、制造、封装等方面精雕细琢。更加自动化和智能化的EDA工具将成为推动Multi-Die系统迅速成长的关键支柱。

不过,仅依靠传统的工具和方法来设计和测试Multi-Die系统,愈发显得有点吃力。近年来,AI在EDA领域的应用无疑为电子设计自动化增添了新的活力。

借助AI技术,Synopsys.ai套件能够迅速应对设计复杂性,承担诸如设计空间探索、验证覆盖范围、回归分析和测试程序生成等重复性任务,同时在功耗、性能和芯片面积方面进行优化。这使得工程师可以将更多精力专注于芯片质量和创新。此外,Synopsys.ai提供业界首个数据流连续解决方案,以加速芯片的设计、验证和批量制造过程。这种基于人工智能的数据分析解决方案使团队能够有效地解锁、连接和分析设计、验证、制造、测试和现场操作中积累的庞大数据量。其独特的芯片监控技术有助于优化功耗、性能、质量、良率和吞吐量,而综合可视化功能则加速了IC生命周期各阶段的根本原因分析。

对于Multi-Die系统中的复杂的多重测试而言,AI驱动的Synopsys TSO.ai将是很好的“助手”。它可以最大限度地降低当今复杂设计的测试成本和上市时间。TSO.ai能够自动在大型测试搜索空间中搜索最佳解决方案,以最大限度地减少模式数量和ATPG周转时间,从而大幅降低测试成本。通过利用人工智能的力量,TSO.ai 提供自动化、可扩展性和专家级生产力,以提供超出手动工作所能达到的结果。

如同Multi-Die技术将多个芯片集合在一起一样,行业的解决方案也不能靠单个的工具来支撑。综合性、平台化、一站式的解决方案方是这个时代的“良药”。在这方面,新思科技的Multi-Die系统解决方案集多种成熟技术于一身。该方案涵盖了架构探索、设计、软件开发、系统验证、IP、测试及芯片生命周期管理等多个方面,正引领着行业从单片系统芯片(SoC)加速向Multi-Die系统的转型。

结语

Multi-Die技术的迅速崛起,不仅是半导体行业技术发展的必然结果,也是市场需求和技术创新相互作用的产物。这一变革背后,是众多芯片行业从业者的辛勤努力和智慧结晶。他们通过精心的设计、创新的思维和EDA工具,共同推动着Multi-Die技术的发展。未来,随着Multi-Die技术的进一步普及和应用,将引领半导体行业走向新的高度,并开启计算技术的新篇章。

上一篇:异构集成 与 异构计算

下一篇:硅基集成光量子芯片技术

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学